# Efficient Distributed Bounded Property Checking

#### Dissertation

der Fakultät für Informations- und Kognitionswissenschaften der Eberhard-Karls-Universität Tübingen zur Erlangung des Grades eines Doktors der Naturwissenschaften (Dr. rer. nat.)

vorgelegt von **Dipl.-Inform. Pradeep Kumar Nalla**aus Hyderabad, Indien

Tübingen 2008

Tag der mündlichen Qualifikation:09.07.2008Dekan:Prof. Dr. M. Prof. Dr. Michael Diehl Prof. Dr. Thomas Kropf Prof. Dr. Wolfgang Rosenstiel 1. Berichterstatter:

2. Berichterstatter:

# Dedicated to Amma and Nanna

First your parents, they give you your life, but then they try to give you their life.

- Chuck Palahniuk

## Acknowledgements

Coming together is a beginning. Keeping together is progress. Working together is success.

- Henry Ford

I would like to thank Prof. Wolfgang Rosenstiel and Prof. Thomas Kropf for giving me the opportunity to do research and pursue Ph.D. studies in Formal Methods Group. In particular, I acknowledge the assistance and logistical support provided by Prof. Rosenstiel. I strongly believe he is the personification of a perfect professor. Apart from technical issues, he also helped me in solving bureucratical issues like VISA extensions, etc. My special thanks to Thomas Kropf. He is impeccable and always talks to the point. Healthy, positive and constructive criticism he does during presentations makes us improving our confidence and lifts our morale. We persons in individual become more tough and do goal oriented research work. He also nurtured how to be a good research scientist. I am grateful to Dr. Jürgen Ruf for his constant encouragement. Ups and downs are all part and parcel of the research. During lows Jürgen was always there for me and supported me. Thanks to his excellent coding skills and the tools he developed. Most of the times, the code he implemented is self-explanatory. Thereby, I learned lot of inside depths of formal verification. My sincere thanks to Dr. Roland J. Weiss for some of his original ideas in my Ph.D. thesis. He motivated me to be more challenging and competitive at work. During his stay in Tübingen, he had inculcated me a sense of responsibility in writing worthful papers and good organizing skills. After all he is a nice human being and made my stay very special at Tübingen. I am particularly grateful to Dipl. Ing. Ingo Kühn. He has inspired and motivated me to do research while I was doing Masters thesis at AMD Saxony, Dresden. My special thanks to all the members of Formal Methods Group (FMG) for the care with which they reviewed the original manuscript of my thesis. In particular, I would like to thank Dr. Prakash Mohan Peranandam. He has assisted me in resolving initial problems of mine concerning research direction. In many ways I have used both his technical and personal experiences. These experiences made my life much easier in Tübingen. I express my deep gratitude also to M.Sc. Djones Lettnin and Dipl. Inf. Jörg Behrend. It was fun working with them. I must acknowledge my colleagues Dipl. Inf. Michael Bensch and Dipl. Inf. Dominik Brugger. Michael was characteristically generous in taking time to review many of my research papers and this thesis. Dominik is truly inspirational figure and he has provided encouragement and ideas in applying concepts from different realms into formal verification of software. I really appreciate the support provided by the folks at Technische Informatik. Their friendship and professional collaboration meant a great deal to me. I really enjoyed their company in ski-seminars, collective outings, afternoon lunch, etc. I must acknowledge my wife for patience and understanding she has shown during final phase of my thesis writing. My special thanks to my sister and her family for supporting and taking care of my parents during my period of stay in Germany. I am thankful to German Research Council (DFG), German Federal Ministry of Education, Science, Research and Technology (BMBF) and Edacentrum for providing financial support to pursue my research studies in Germany. Last but not least, thanks to www.google.com(/de) and www.wikipedia.com(/de). They made our life much easier to access the enormous amount of information through world wide web.

Finally I would like to make a note: *It has been a very long journey I have taken, but a very fulfilling one.*

#### **Abstract**

Today, verification of industrial size designs like multi-million gate ASICs (Application Specific Integrated Circuit) and SoC (System-on-a-Chip) processors consumes up to 75% of the design effort. The trend to augment functional verification with formal verification tries to alleviate this problem. Efficient property checking algorithms based on binary decision diagrams (BDDs) and satisfiability (SAT) solvers allow the automatic verification of medium-sized designs. However, the steadily increasing design sizes still leave verification as the major bottleneck, because formal methodologies do not yet scale to very large designs.

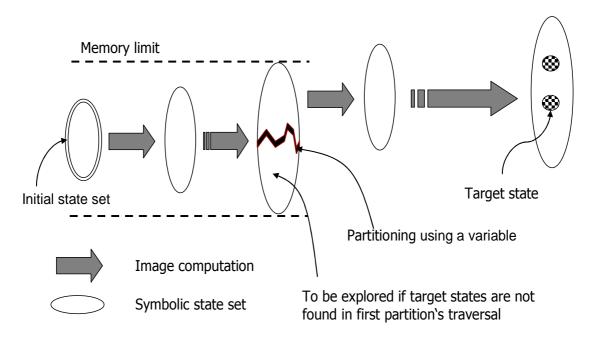

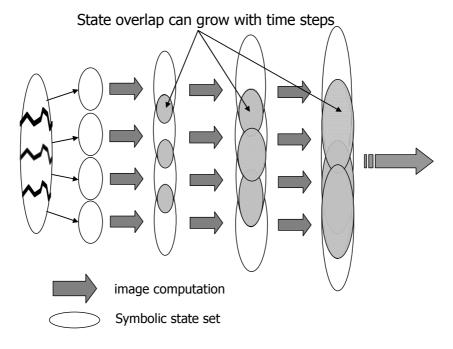

To address these problems researchers came up with the idea of combining symbolic simulation and bounded model checking on-the-fly. The current tools pioneer in handling comparatively larger designs by partitioning the state set and they can be represented using partitioned ordered BDDs (POBDDs). These partitions will be explored in a divide-and-conquer manner. However, still they face memory exhaustion for very large models due to the BDD explosion problem. Even the SAT based bounded model checking (BMC) can search up to a maximum depth allowed by the physical memory on a single server. These observations motivated the parallelization of symbolic state space traversal algorithms. Distributed algorithms verify larger models and return results faster than sequential versions. Existing schemes for parallelizing BDD-based verification algorithms often suffer from state overlap or duplicate work, cross over states among partitions, inefficient work distribution, improper load balancing, synchronicity and communication overhead. The algorithms concentrate heavily either on reachability (validation) or falsification but not both together.

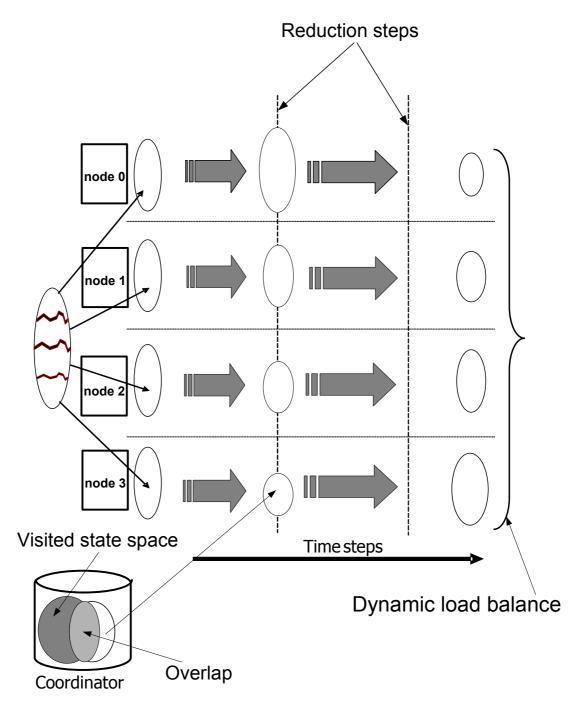

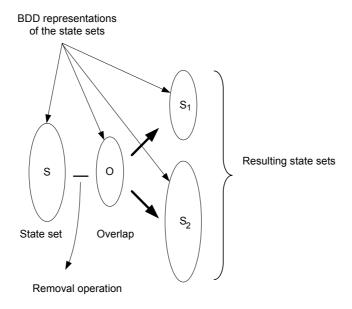

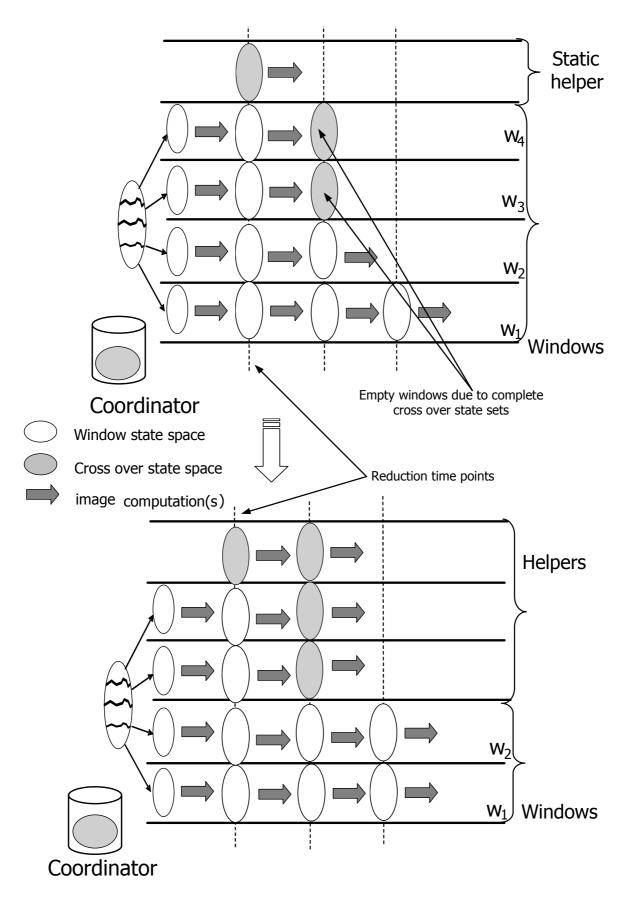

My main contributions include a *dynamic overlap reduction* and a *hybrid* distributed algorithms. The dynamic overlap reduction technique smoothens the state space traversal of each network node by removing the state overlap that it suffers from. The removal of overlap works in an asynchronous manner, i.e., with out waiting for other processors to complete their image computations. This method has the natural side effect of dynamic load balancing among network nodes, i.e., the nodes that deal with a large state space at one time point will be later assigned a small state space and vice versa. Since all the nodes perform asynchronous state space traversal on their whole state subsets, the method is best suitable for validation.

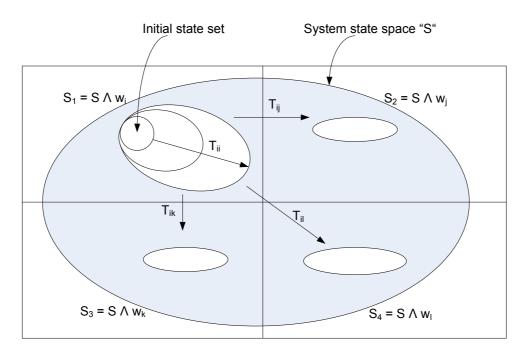

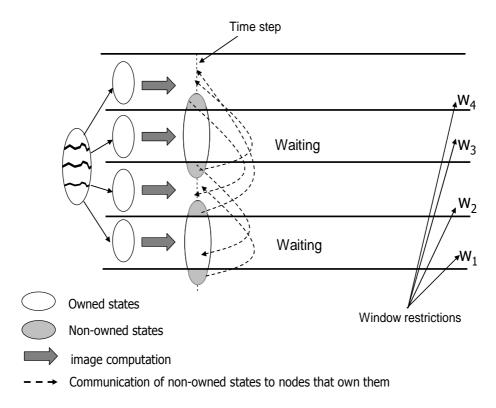

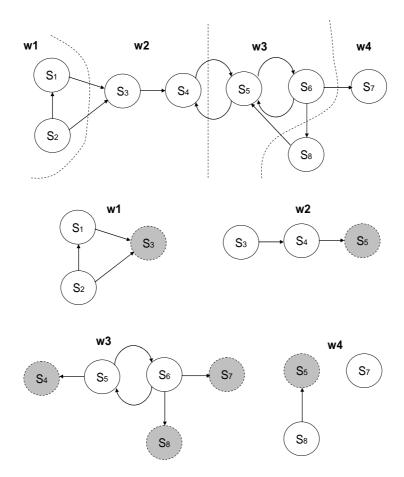

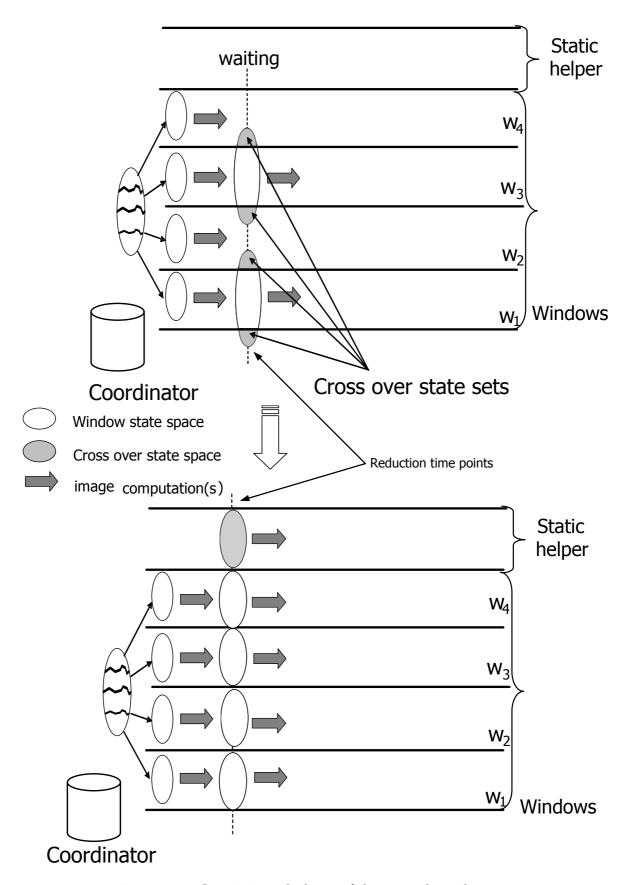

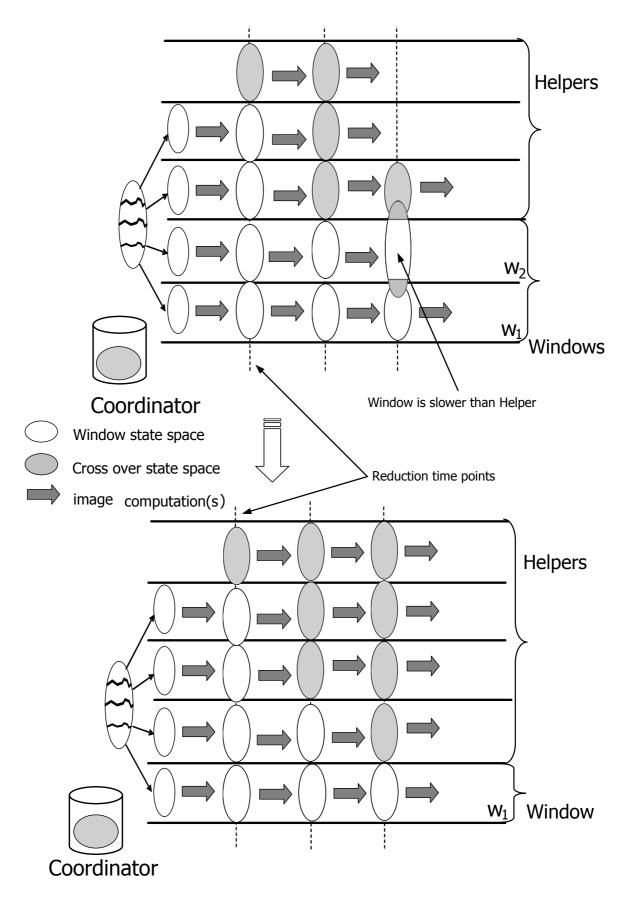

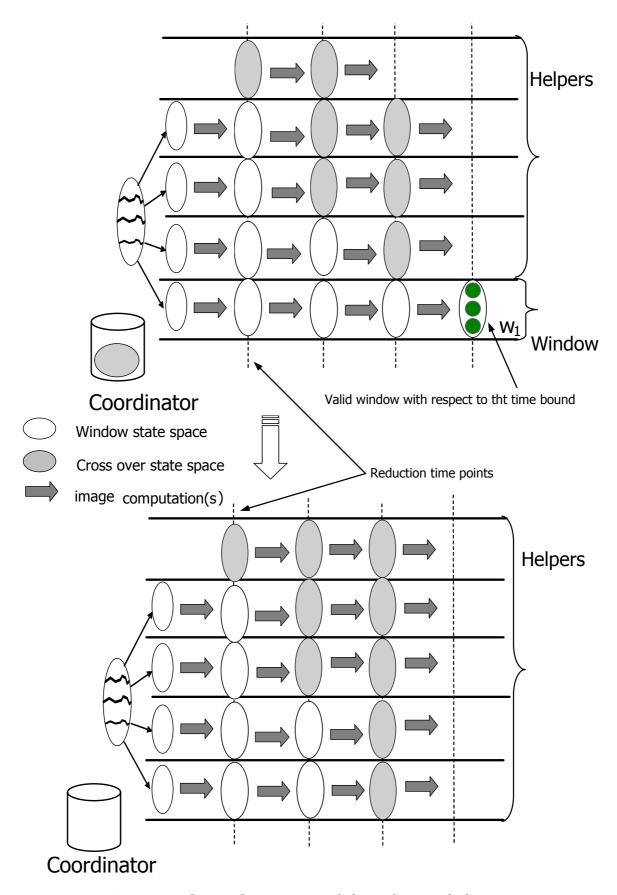

The hybrid method is an asynchronous distributed algorithm, suited for both fast error detection and complete validation. This approach combines well known windowing and dynamic overlap reduction techniques. The windowing technique has partitions that are identified by unique combination of variables. Each window restricts its state space at regular intervals to keep the reachable state space within it's window region. The real state space is discriminated by the window as owned and non-owned states. The nodes on the cluster machine are employed

with two different types of tasks. Some nodes, windows aim at faster falsification on the basis of the windowing technique. The other type of nodes called helpers are intending for validation on the basis of the dynamic overlap reduction. All the network nodes asynchronously traverse their local state spaces for both error states detection and reachability of a time bound. Thus, the hybrid algorithm efficiently combines both windowing and dynamic overlap reduction techniques to obtain more synergy and gains the advantages of using both the approaches. Further, the algorithm expedites the verification process by reassigning the work to idle nodes as quickly as possible. As a result it avoids the wasted computation power and makes the system work efficient.

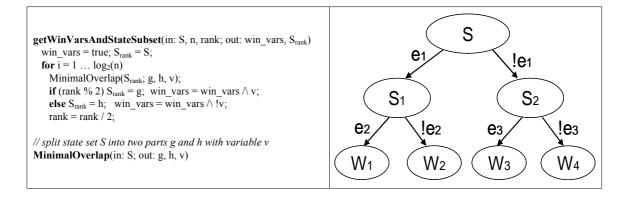

The dynamic overlap reduction and hybrid algorithms are best suitable for homogeneous system configurations like a cluster. However, this thesis also presents a grid-based parallelization algorithm which is suitable for fast falsification of very large designs. In addition, all the parallel algorithms in this thesis partition the state space using the *Minimal overlap* algorithm which pioneers in statically minimizing the cross over states or state overlap among the partitions.

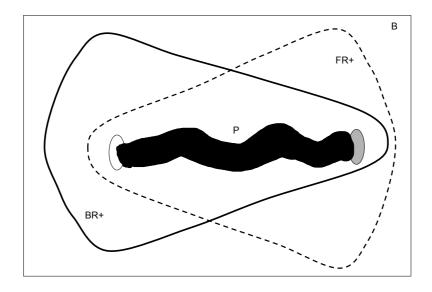

The parallel algorithms speedup the distributed verification and automatically checks the correctness of very large hardware designs. The distributed computation shows approximately linear speedups in execution time and enables faster verification of properties. As a supplement, this thesis also presents a novel distributed algorithm, which uses mixed forward and backward traversal mechanism for Black Box verification.

#### Zusammenfassung

Heutzutage benötigt die Verifikation von industriellen Designs wie z.B. ASICs (Application Specific Integrated Circuit) und SoC (System-on-a-Chip) bis zu 75 % der Entwicklungskosten. Der Trend funktionale Verifikation durch formale Verifikation zu erweitern versucht dieses Problem zu lösen. Effiziente Algorithmen basierend auf BDDs (Binary Decision Diagrams) und SAT (Satisfiability) erlauben die automatische Verifikation von mittelgroßen Designs. Durch die ständig wachsenden Designgrößen bleibt die Verifikation trotzdem der Flaschenhals, da formale Methoden noch nicht für sehr große Designs skalieren.

Um diese Probleme zu beheben wurde in der Forschung die Idee entwickelt symbolic simulation und bounded model checking direkt zu kombinieren. Aktuelle Tools sind in der Lage vergleichsweise große Designs durch Partitionierung des Zustandsraums zu bewältigen. Der Zustandsraum wird dabei auf partitionierte geordnete BDDs (POBDDs) abgebildet und mit einer Teile-und-Herrsche Strategie durchsucht. Trotzdem kämpfen diese Tools immer noch mit Speicherproblemen bei sehr großen Modellen bedingt durch den bei BDDs auftretenden Speicherüberlauf. Auch SAT-basierende bounded model checking Tools (BMC) sind in der Suchtiefe beschränkt, durch den physikalisch zur Verfügung stehenden Hauptspeicher eines einzelnen Rechenknotens. Diese Beobachtungen motivierten die Parallelisierung der Algorithmen zur Traversierung von symbolischen Zustandsräumen. Die verteilten Algorithmen können größere Modelle verifizieren und liefern die Ergebnisse schneller als die sequentiellen Versionen. Existierende Methoden zur Parallelisierung von BDD-basierenden Verifikationsalgorithmen kämpfen oft mit Zustandsraumüberlappungen, ineffizienter Verteilung schlechter Lastbalancierung, sowie Synchronisierungs- und Kommunikations-Overhead. Die Algorithmen konzentrieren sich entweder auf Erreichbarkeit (Validierung) oder auf das schnelle Finden von Fehlern aber nicht auf beides zusammen.

Meine Hauptarbeit beinhaltet eine dynamische Reduzierung der Überlappung (dynamic overlap reduction) und einen hybriden verteilten Algorithmus. Die Technik zur dynamischen Reduzierung von Überlappungen verbessert die Traversierung des Zustandsraumes von jedem Rechenknoten durch Reduzierung der Überlappungen. Die Überlappungs-Reduzierung arbeitet asynchron d.h. ohne zu warten bis andere Knoten ihre Image Berechnung beendet haben. Diese Methode hat den natürlichen Seiteneffekt der dynamischen Lastbalancierung zwischen den Netzwerkknoten, d.h. die Knoten, die zu Beginn einen großen Teil des Zustandsraums bekommen, werden im nächsten Durchlauf einen kleineren Teil bekommen und vice versa. Da alle Knoten eine asynchrone Exploration ihres eigenen Zustandsraums durchführen ist diese Methode sehr gut zur Validierung geeignet.

Bei der hybriden Methode handelt es sich um einen asynchronen verteilten Algorithmus, der sowohl geeignet ist zum schnellen Auffinden von Fehlern als auch zur vollständigen Verifikation. Der Ansatz kombiniert bereits bekannte windowing und dynamic overlap reduction Techniken. Der windowing Ansatz benutzt

Partitionen, die durch eindeutige Variablenkombinationen identifiziert werden. Jedes window beschränkt seinen Zustandsraum in unregelmäßigen Abständen, um den Erreichbaren Zustandsraum in den eigenen window Grenzen zu halten. Der gesamte Zustandsraum wird eingeteilt in benutzte und noch nicht benutzte Zustände. Den Knoten des Rechen-Clusters werden zwei unterschiedliche Aufgaben zugeteilt. Einige Knoten, windows, versuchen schnell Fehler zu finden auf Basis der windowing Technik. Der andere Typ von Knoten, helper, versucht zu validieren auf Basic der dynamischen Überlappungs-Reduzierung. Alle Netzwerkknoten traversieren asynchron ihren lokalen Zustandsraum mit zwei Zielen: auffinden von Fehlerzuständen und Erreichbarkeit einer Zeitschranke. Somit kombiniert der hybride Algorithmus auf effiziente Weise sowohl windowing als auch dynamische Überlappungs-Reduzierung, um dadurch mehr Synergien zu erzeugen und um die Vorteile beider Methoden zu nutzen. Der Algorithmus beschleunigt außerdem den Verifikationsprozess durch ein so schnell wie möglich erneute Verteilung der Arbeit auf im Leerlauf befindliche Knoten. Als Ergebnis wird dadurch die Verschwendung von Rechenleistung verhindert und die Effizienz des Systems gesteigert.

Beide Ansätze sind bestens geeignet für homogene System-Konfigurationen wie z.B. Cluster. Außerdem wird innerhalb der Dissertation auch ein Grid-basierender Algorithmus vorgestellt, welcher für die schnelle Fehlersuche in großen Entwürfen geeignet ist. Zusätzlich benutzen alle parallelen Algorithmen in dieser Dissertation den *Minimal overlap* Algorithmus welcher eine statische Minimierung der Kreuz-Überlappungs-Zustände bzw. der Überlappungszustände zwischen den Partitionen durchführt.

Die parallelen Algorithmen beschleunigen die verteilte Verifikation und überprüfen automatisch die Korrektheit von sehr großen Hardware-Designs. Die verteilte Berechnung zeigt annähernd linearen Speedup in der Ausführungszeit und ermöglicht die schnellere Verifikation von Eigenschaften. Als Ergänzung dieser Arbeit wird ein neuer verteilter Algorithmus präsentiert, welcher einen gemischten Vorwärts- und Rückwärts traversierungs-Mechanismus benutzt zur Black-Box-Verifikation.

# **Contents**

| 1 | Intr       | oductio | on                         | 1    |

|---|------------|---------|----------------------------|------|

|   | 1.1        | What    | is Verification            | . 1  |

|   | 1.2        | Simul   | lation                     | . 2  |

|   | 1.3        | Forma   | al Verification            | . 3  |

|   |            | 1.3.1   | Equivalence Checking       | . 4  |

|   |            | 1.3.2   | Theorem Proving            | . 4  |

|   |            | 1.3.3   | Model Checking             | . 4  |

|   |            | 1.3.4   | State Explosion Problem    | . 7  |

|   |            | 1.3.5   | Thesis Focus               | . 8  |

|   |            | 1.3.6   | Distributed Verification   | . 8  |

|   | 1.4        | Thesis  | s Structure                | . 10 |

| _ | <b>.</b> . |         |                            |      |

| 2 |            | iminar  |                            | 12   |

|   | 2.1        | Boolea  | an Functions               | . 12 |

|   |            | 2.1.1   | Support Set                | . 12 |

|   |            | 2.1.2   | Minterms                   | . 13 |

|   |            | 2.1.3   | Cofactor                   | . 13 |

|   |            | 2.1.4   | Shannon Expansion          | . 13 |

|   |            | 2.1.5   | Generalized Cofactor       | . 13 |

|   | 2.2        | Finite  | State Machines             | . 14 |

|   | 2.3        | Binary  | y Decision Diagrams (BDDs) | . 14 |

|   |            | 2.3.1   | Notations                  | . 16 |

|   |            | 2.3.2   | Partitioned-ROBDDs         | . 16 |

|   | 2.4        | Tempo   | oral Logics                | . 18 |

|   |            | 2.4.1   | CTL*                       | . 18 |

|   |            | 2.4.2   | CTL                        | . 19 |

|   |      | 2.4.3                                                                                                        | LTL                                                                                                                                                                                                                                                                                                                                                             | 20                                                             |

|---|------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|   |      | 2.4.4                                                                                                        | Application of Temporal Logics to Formal Verification                                                                                                                                                                                                                                                                                                           | 20                                                             |

|   | 2.5  | Symbo                                                                                                        | olic State Machine Traversal                                                                                                                                                                                                                                                                                                                                    | 21                                                             |

|   |      | 2.5.1                                                                                                        | Transition Relation                                                                                                                                                                                                                                                                                                                                             | 21                                                             |

|   |      | 2.5.2                                                                                                        | Image and Pre-image Computations                                                                                                                                                                                                                                                                                                                                | 22                                                             |

|   |      | 2.5.3                                                                                                        | The Traversal Algorithm                                                                                                                                                                                                                                                                                                                                         | 23                                                             |

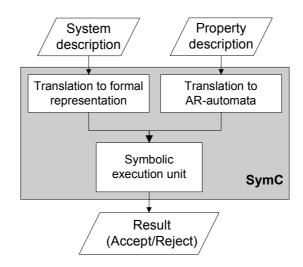

|   | 2.6  | Forma                                                                                                        | al Bounded Property Checking Tool - SymC                                                                                                                                                                                                                                                                                                                        | 24                                                             |

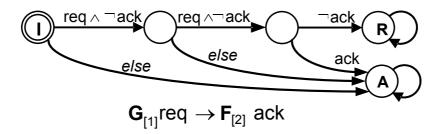

|   |      | 2.6.1                                                                                                        | FLTL and AR-automata                                                                                                                                                                                                                                                                                                                                            | 24                                                             |

|   |      | 2.6.2                                                                                                        | AR-automata                                                                                                                                                                                                                                                                                                                                                     | 26                                                             |

|   |      | 2.6.3                                                                                                        | SymC Overview                                                                                                                                                                                                                                                                                                                                                   | 27                                                             |

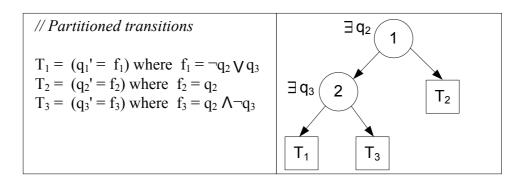

|   |      | 2.6.4                                                                                                        | Optimizations                                                                                                                                                                                                                                                                                                                                                   | 28                                                             |

|   | 2.7  | Partiti                                                                                                      | oned Based Traversal                                                                                                                                                                                                                                                                                                                                            | 30                                                             |

|   | 2.8  | Black                                                                                                        | Box Verification                                                                                                                                                                                                                                                                                                                                                | 30                                                             |

|   |      | 2.8.1                                                                                                        | Verification Goals                                                                                                                                                                                                                                                                                                                                              | 31                                                             |

|   |      | 2.8.2                                                                                                        | Transition Types                                                                                                                                                                                                                                                                                                                                                | 32                                                             |

| 2 | Ctat | ( 11-                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                 | 22                                                             |

| 3 |      | e-of-the                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                 | 33                                                             |

|   | 3.1  | Seque                                                                                                        | ntial Based Optimizations                                                                                                                                                                                                                                                                                                                                       | 33                                                             |

|   |      | 011                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                 | 00                                                             |

|   |      | 3.1.1                                                                                                        | Symbolic Verification Using Partitioning Techniques                                                                                                                                                                                                                                                                                                             | 33                                                             |

|   |      | 3.1.2                                                                                                        | Mixed Traversals                                                                                                                                                                                                                                                                                                                                                | 35                                                             |

|   |      | 3.1.2<br>3.1.3                                                                                               | Mixed Traversals                                                                                                                                                                                                                                                                                                                                                | 35<br>36                                                       |

|   |      | 3.1.2<br>3.1.3<br>3.1.4                                                                                      | Mixed Traversals                                                                                                                                                                                                                                                                                                                                                | 35<br>36<br>37                                                 |

|   |      | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5                                                                             | Mixed Traversals                                                                                                                                                                                                                                                                                                                                                | 35<br>36<br>37<br>39                                           |

|   |      | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6                                                                    | Mixed Traversals                                                                                                                                                                                                                                                                                                                                                | 35<br>36<br>37<br>39<br>39                                     |

|   |      | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7                                                           | Mixed Traversals                                                                                                                                                                                                                                                                                                                                                | 35<br>36<br>37<br>39<br>39                                     |

|   | 3.2  | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>Distrib                                                | Mixed Traversals                                                                                                                                                                                                                                                                                                                                                | 35<br>36<br>37<br>39<br>39<br>40<br>40                         |

|   | 3.2  | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>Distrib<br>3.2.1                                       | Mixed Traversals  Symmetry Reduction and Underapproximation  State-of-the-art Black Box Verification  Guided Search  Multithreaded Reachability  Partitioning in SymC  outed Verification  Distributed Explicit Model Checking                                                                                                                                  | 35<br>36<br>37<br>39<br>39<br>40<br>40<br>40                   |

|   | 3.2  | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>Distrib<br>3.2.1<br>3.2.2                              | Mixed Traversals  Symmetry Reduction and Underapproximation  State-of-the-art Black Box Verification  Guided Search  Multithreaded Reachability  Partitioning in SymC  Outed Verification  Distributed Explicit Model Checking  Distributed SAT and SAT based BMC                                                                                               | 35<br>36<br>37<br>39<br>39<br>40<br>40<br>40                   |

|   | 3.2  | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>Distrib<br>3.2.1<br>3.2.2<br>3.2.3                     | Mixed Traversals  Symmetry Reduction and Underapproximation  State-of-the-art Black Box Verification  Guided Search  Multithreaded Reachability  Partitioning in SymC  outed Verification  Distributed Explicit Model Checking  Distributed SAT and SAT based BMC  Distributed Symbolic Reachability                                                            | 35<br>36<br>37<br>39<br>39<br>40<br>40<br>40<br>41             |

|   |      | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>Distrib<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4            | Mixed Traversals                                                                                                                                                                                                                                                                                                                                                | 35<br>36<br>37<br>39<br>39<br>40<br>40<br>40<br>41<br>41<br>41 |

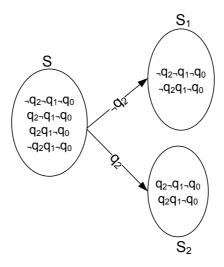

|   | 3.2  | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>Distrib<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>Partiti | Mixed Traversals  Symmetry Reduction and Underapproximation  State-of-the-art Black Box Verification  Guided Search  Multithreaded Reachability  Partitioning in SymC  Distributed Verification  Distributed Explicit Model Checking  Distributed SAT and SAT based BMC  Distributed Symbolic Reachability  Grid-based Bounded Model Checking  oning Heuristics | 35<br>36<br>37<br>39<br>39<br>40<br>40<br>40<br>41<br>41<br>43 |

|   |      | 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>Distrib<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4            | Mixed Traversals                                                                                                                                                                                                                                                                                                                                                | 35<br>36<br>37<br>39<br>39<br>40<br>40<br>40<br>41<br>41<br>41 |

|   |      | 3.3.3    | Eager Decomposition                               | 45 |

|---|------|----------|---------------------------------------------------|----|

|   |      | 3.3.4    | Minimal Overlap                                   | 45 |

|   |      | 3.3.5    | Guiding Heuristics                                | 46 |

|   | 3.4  | Un-ac    | ddressed Problems                                 | 47 |

|   |      | 3.4.1    | State-of-the-art Sequential Problems              | 47 |

|   |      | 3.4.2    | State-of-the-art Parallel Problems                | 49 |

|   | 3.5  | Contr    | ibutions                                          | 52 |

| 4 | Para | alleliza | tion                                              | 55 |

|   | 4.1  | Parall   | elization of a Symbolic Bounded Property Checking | 55 |

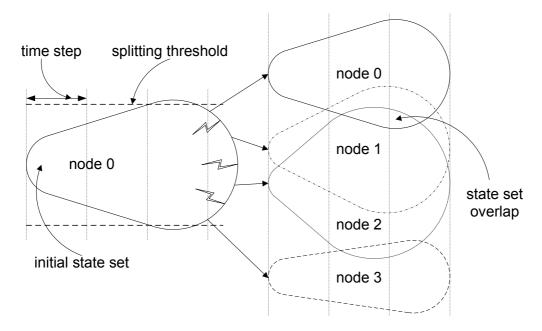

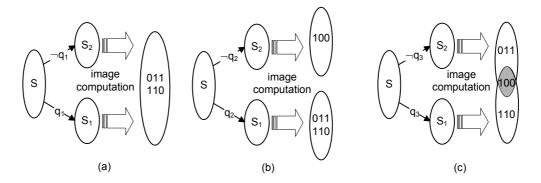

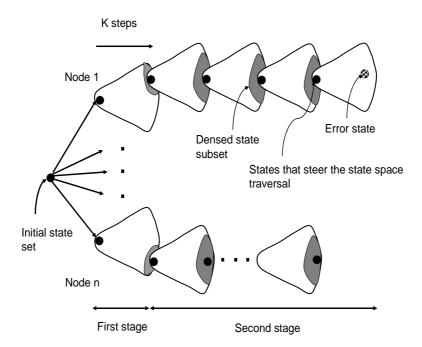

|   |      | 4.1.1    | State Set Decomposition in Parallel               | 56 |

|   |      | 4.1.2    | Counterexample Computation                        | 58 |

|   |      | 4.1.3    | State Set Overlap                                 | 59 |

|   | 4.2  | Concl    | usion                                             | 60 |

| 5 | Trea | tments   | s for State Set Overlap                           | 62 |

|   | 5.1  | Overl    | ap Reduction                                      | 62 |

|   |      | 5.1.1    | Static Overlap Reduction                          | 63 |

|   | 5.2  | Distri   | buted Checking Algorithm                          | 65 |

|   |      | 5.2.1    | Dynamic Overlap Reduction                         | 66 |

|   |      | 5.2.2    | Counterexample Computation                        | 70 |

|   |      | 5.2.3    | Limitations of Dynamic Overlap Reduction Method   | 72 |

|   | 5.3  | Concl    | usion                                             | 72 |

| 6 | Hyb  | orid Di  | stributed Approach                                | 74 |

|   | 6.1  | Metho    | odology                                           | 74 |

|   |      | 6.1.1    | Window States and Cross over States               | 75 |

|   | 6.2  | The D    | Distributed Algorithm                             | 77 |

|   |      | 6.2.1    | Window Node Algorithm                             | 78 |

|   |      | 6.2.2    | Helper Node Algorithm                             | 79 |

|   |      | 6.2.3    | Coordinator Node Algorithm                        | 79 |

|   | 6.3  | Coun     | terexample Computation                            | 80 |

|   | 6.4  | Wind     | ow Variable Selection                             | 81 |

|   |      | 6.4.1    | Partitioning Algorithm                            | 81 |

|    | 6.5                                       | Concl          | usion                                                         | 82  |

|----|-------------------------------------------|----------------|---------------------------------------------------------------|-----|

| 7  | Gric                                      | l-based        | Fast Falsification                                            | 90  |

|    | 7.1                                       | Why (          | Grid                                                          | 90  |

|    |                                           | 7.1.1          | Grid Computing Overview                                       | 90  |

|    |                                           | 7.1.2          | Grid Application                                              | 91  |

|    | 7.2                                       | Grid-b         | pased Distribution Algorithm                                  | 91  |

|    |                                           | 7.2.1          | Underapproximation using Guiding Algorithms                   | 94  |

|    | 7.3                                       | Concl          | usion                                                         | 95  |

| 8  | Parallelization of Black Box Verification |                |                                                               | 96  |

|    | 8.1                                       | Black          | Box Verification                                              | 96  |

|    |                                           | 8.1.1          | Why Parallelization                                           | 97  |

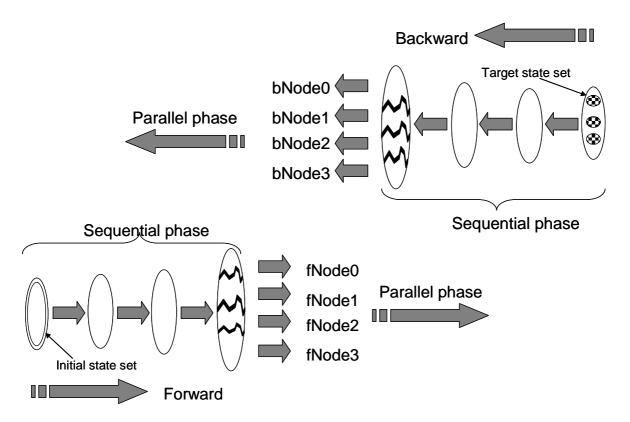

|    | 8.2                                       | Comb<br>Platfo | ination of Forward and Backward Traversal on a Distributed rm | 97  |

|    |                                           | 8.2.1          | Backward Node Algorithm                                       | 99  |

|    |                                           | 8.2.2          | Forward Node Algorithm                                        | 101 |

|    |                                           | 8.2.3          | Coordinator Node Algorithm                                    | 103 |

|    | 8.3                                       | Concl          | usion                                                         | 105 |

| 9  | Imp                                       | lement         | ration                                                        | 106 |

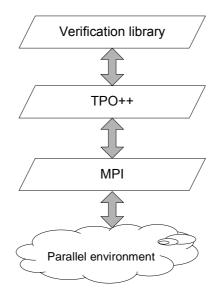

|    | 9.1                                       | Ingred         | lients Needed for the Parallelization                         | 106 |

|    | 9.2                                       | Data 7         | Transmission                                                  | 107 |

|    |                                           | 9.2.1          | Blocking Communication                                        | 107 |

|    |                                           | 9.2.2          | User-defined BDD Data Type                                    | 109 |

|    | 9.3                                       | BDD 7          | Transmission                                                  | 111 |

|    |                                           | 9.3.1          | BDDs to Sequence of Bytes Conversion                          | 111 |

|    |                                           | 9.3.2          | BDDs Construction From Sequence of Bytes                      | 112 |

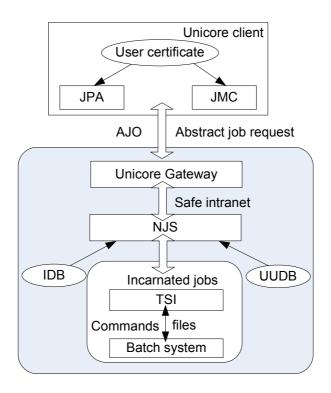

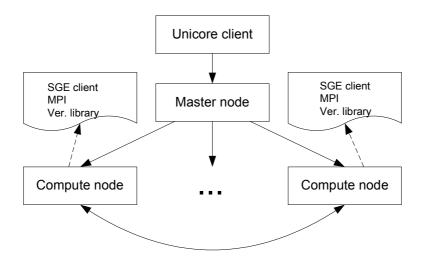

|    | 9.4                                       | The G          | rid Framework                                                 | 114 |

|    |                                           | 9.4.1          | UNICORE                                                       | 114 |

|    | 9.5                                       | Concl          | usion                                                         | 116 |

| 10 | Expe                                      | erimen         | tal Results                                                   | 117 |

|    | 10.1                                      | Detail         | s of Experiments                                              | 117 |

|    |                                           | 10 1 1         | Parallel Environment                                          | 117 |

|    |      | 10.1.2  | Implementation Details              |

|----|------|---------|-------------------------------------|

|    |      | 10.1.3  | Checked Designs                     |

|    |      | 10.1.4  | Checked Properties                  |

|    | 10.2 | Verific | ation Using a Single Processor      |

|    | 10.3 | Distrib | outed Verification                  |

|    |      | 10.3.1  | Basic Parallelization               |

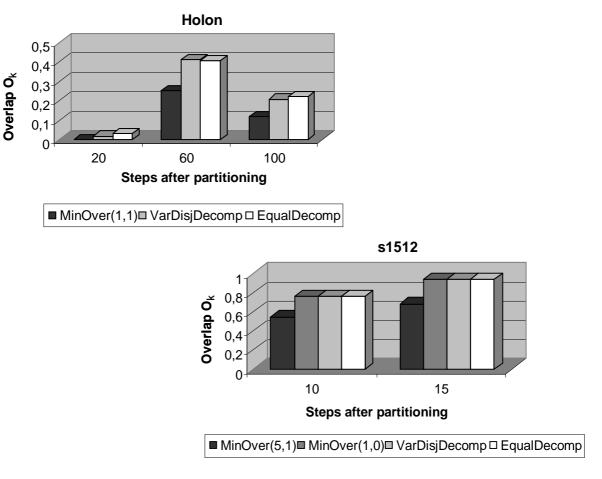

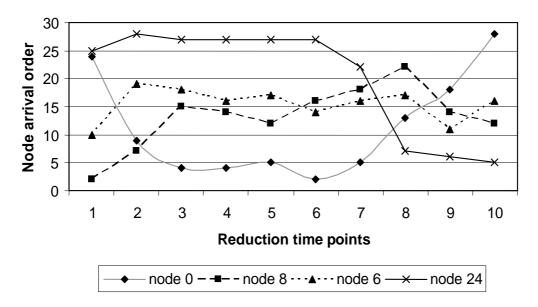

|    |      | 10.3.2  | Dynamic Overlap Reduction           |

|    |      | 10.3.3  | Hybrid vs Dynamic Overlap Reduction |

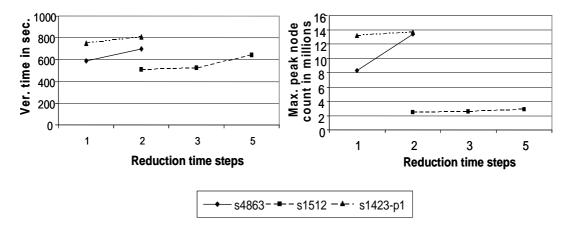

|    |      | 10.3.4  | Variable Ordering Comparison        |

|    | 10.4 | State-c | of-the-art Comparison               |

|    |      | 10.4.1  | Falsification                       |

|    |      | 10.4.2  | Reachability                        |

|    | 10.5 | Grid-b  | pased Fast Falsification            |

|    |      | 10.5.1  | Grid Configuration                  |

|    |      | 10.5.2  | Discussion                          |

| 11 | Con  | clusion | as and Future Work 13'              |

|    | 11.1 | Conclu  | asions                              |

|    |      | 11.1.1  | Benefits to the Industry            |

|    | 11.2 | Future  | e Work                              |

## Chapter 1

## Introduction

In my experience, there is only one motivation, and that is desire. No reasons or principle contain it or stand against it.

- Jane Smiley

The increasing importance of automated formal verification in industry is driving a growing interest in those aspects that directly impact the applicability to real world problems. One of the main technical challenges lies in devising tools or methodologies that allow to handle large design state spaces. Over the last years various approaches have been developed. Recently, an increasing interest in parallel and distributed verification has been emerged. Parallel processing can help speedup the verification process by providing many CPUs that can work on the problem. The aim of this thesis is to enable efficient distributed verification by minimizing the problems that would come across during parallel verification.

This chapter first introduces the basic concepts of verification. Second, it explicates different forms of verification and their differences. Third, it details the prevalent problem faced by the formal verification. Next, it discusses the form of verification this thesis focuses on and details the thesis synopsis. Finally, it gives an exposition on distributed verification and factors that influence the effectiveness of verification in a distributed environment.

## 1.1 What is Verification

Today, hardware and software systems are widely used in applications where failure is unacceptable [1]. Recent examples of such notorious failures are available in [2, 3]. These failures can range from mild annoyance to major catastrophes and the cost - to individuals, to companies, to society as a whole - can likewise be immense [4]. These hazards result from the fact that the relentless increase in technology allows us to produce increasingly complex designs, which contain an increasing number of bugs. Therefore, the need for reliable hardware or software systems is critical. Verification is a process used to demonstrate the functional

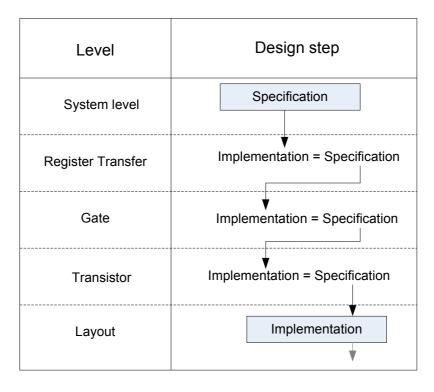

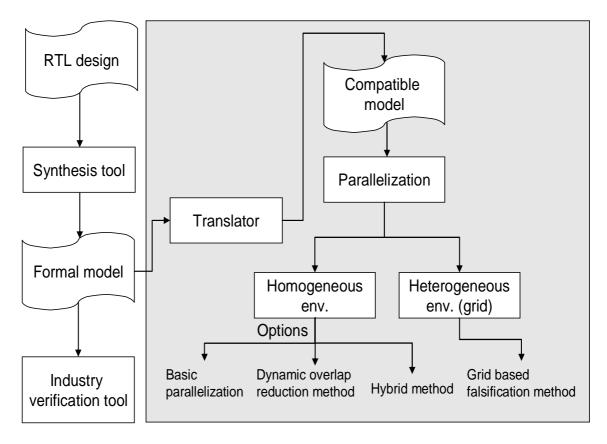

Figure 1.1: Design flow.

correctness of a design. However, today in the era of multi-million gate Application Specific Integrated Circuits (ASICs), reusable Intellectual Properties (IP), System-on-a-Chip (SoC) designs, verification consumes up to 70% of the design effort and the code that implements the verification process makes up to 80% of the total design project code volume [5]. The principal verification methods for complex systems are simulation and formal verification. Simulation checks whether the design exhibits the proper behavior as elicited by a series of functional tests, whereas formal verification uses formal proofs to demonstrate the validity of a design against formal specification. Fig. 1.1 demonstrates the typical refinement principle of circuit design. The design process is divided into several steps, where the implementation resulting on a certain abstraction level is used as the specification for the next lower one [6]. The verification task at each level is to check the implementation against a specification. The register transfer level (RTL) of the circuit is typically described using hardware description languages (HDLs) like Verilog and VHDL.

## 1.2 Simulation

The conventional verification method to discover design errors is *simulation*. The design is usually described using a hardware description language, which can be simulated. Input sequences are created which reflect the critical execution traces of the design to examine the design functionality. However, in order to get full confidence in the design we would have to perform a complete simulation which

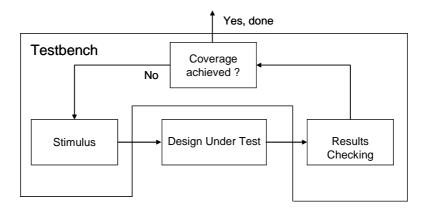

Figure 1.2: Overview of a testbench.

covers all possible input combinations. In case of sequential circuits, the number of input sequences increases exponentially with the number of inputs and the circuit states, it is a laborious task even for designs of moderate size to exercise all possible input sequences. This problem is typically referred as the incomplete *coverage* problem. Simulation consists of four major tasks: 1. Generating the functional tests; 2. Executing the test stimulus on the design; 3. Determining if the design behavior satisfies its specification during the execution; 4. Collecting coverage statistics. The second task, execution, is performed by a simulator. The other three tasks are performed by a testbench. The key ingredients of a testbench are shown in Fig. 1.2. Nowadays, people are combining temporal assertions with simulation, for example in [7, 8, 9, 10]. Temporal assertions are properties based on time that are evaluated within an execution engine, i.e., a simulator. Verification based on assertions is known as assertion-based verification methodology. It has the ability to monitor internal signals and catch violations locally. Furthermore, it improves observability and debug ability. In many ways it is different from a pure testbench based verification methodology, where output sequences are manually checked against the specification. It leverages the power of formal verification by adopting some internal formal semantics.

## 1.3 Formal Verification

Formal verification is the act of proving correctness of a system with respect to a formal specification or a *property* using formal methods. In contrast to traditional simulation, it covers exhaustively all the possible executions of a system. However, formal verification can be further divided into three broad categories: *equivalence checking*, *theorem proving*, and *model checking*. Because of the *coverage* problems in *simulation*, formal verification plays a complementary role as far as the whole verification process is concerned.

## 1.3.1 Equivalence Checking

Equivalence checking is a process of comparing two circuits supposed to have identical behavior in order to verify the correctness of logic optimization, register retiming, state re-encoding, etc. The problem of *equivalence checking* can be converted into the problem of reachable states of the product state machine. Given two state machines to compare, the equivalence checking process ties the input lines of both machines together, sends the outputs to a comparator and provides the clock. This combination is just another bigger state machine. The original two state machines have identical behavior if and only if the new state machine indicates the outputs are equal for all reachable states [1]. However, the complexity of *equivalence checking* continues to increase exponentially with the design size.

## 1.3.2 Theorem Proving

In theorem proving, the design and the properties are expressed as formulas by using mathematical logic. A property is proved if it can be derived from the design using a set of axioms and inference rules. Sometimes the proof consists of intermediate definitions and lemmas in addition to the axioms and rules. Although theorem proving has several applications like software verification [11, 12, 13], mathematics, and security/cryptographic protocols, it requires a great deal of skilled human guidance due to insufficient automation. For example, if theorem prover uses first order or higher order logic then proof problems are semi-decidable or undecidable and human guiding is needed. In addition, it lacks support for digital design languages and is hard to compose systems and proofs.

## 1.3.3 Model Checking

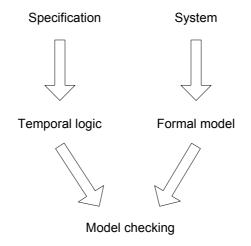

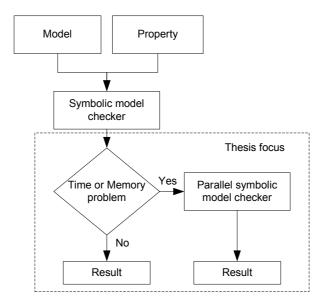

Applying model checking [1, 14] to a design consists of two main tasks *modelling* and *specification*. The task *modelling* is to covert a system or design into a formalism, typically an FSM, accepted by a model checking tool. It require the use of abstraction techniques to eliminate unimportant details of the system. The *specification* is usually given in *temporal logic*. A *temporal logic* is a formal language to express properties changing over time. Most predominantly used temporal logics are Computation Tree Logic (CTL) and Linear Time Temporal Logic (LTL) [15]. Each logic has its own expressive capabilities. The detailed explanation on these logics is postponed to the next chapter. Model checking provides a means to check whether the model of the design satisfies a given specification. There are two main paradigms for model checking: explicit state model checking and symbolic model checking. Fig. 1.3 visualizes an overview of a model checking process.

Figure 1.3: Overview of a model checking process.

#### 1.3.3.1 Explicit State Model Checking/Enumerative Model Checking

Explicit state model checking uses an explicit representation of the system's global state graph, usually given by a state transition function. An explicit state model checker evaluates the validity of the temporal properties over the model by interpreting its global state transition graph. The property validation amounts to a partial or complete exploration of the state space. During the exploration the explicit model checker treats states one by one. Tools like SPIN [16] and PV [17] are well known explicit model checkers.

#### 1.3.3.2 Symbolic Model Checking

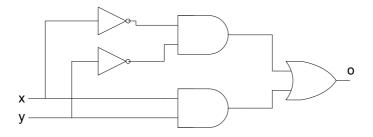

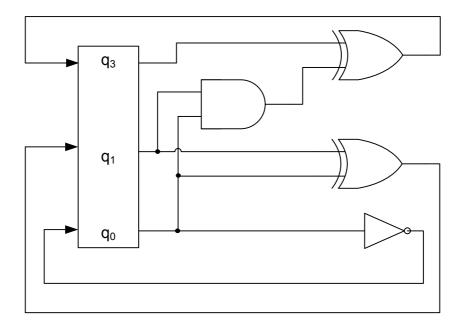

Symbolic simulation [18] combines conventional simulation with symbolic methods. The advantage of conventional simulation is accuracy, but it needs one simulation vector at a time. In Fig. 1.4, we would require four simulation runs with inputs 00, 01, 10 and 11. Symbolic simulation adds two innovations to conventional logic simulations [19]. The first innovation of a third logic value X represents the *unknown* value. Setting an input to X gives the effect of simulating the circuit with both 0 and 1. As a result, one can reduce the number of simulation runs. However, the value X loses information. In Fig. 1.4 setting one or both inputs to X yields an X at the output, which is an futile result for verification. The simulation with values X, is called as X-simulation. The prominent second innovation is the symbolic simulation. In contrast to X-simulation, symbolic simulation assigns a symbolic value for each input in the design, that can be either 0 or 1, rather than to a constant 0,1 or X. The symbolic simulator computes symbolic expressions for each output in terms of input variables. In Fig. 1.4, assume we set input x to 1 and input y to the symbolic value z. The symbolic simulator would then calculate that the upper AND gate will set to 0 and lower AND gate will set to symbolic value z. Finally, the OR gate will settle to z. Thus, we have effectively run two simulation vectors (*xy* equal to 10 and 11) and computed the output as a function

Figure 1.4: A simple XNOR circuit.

of symbolic values. Typically, a BDD (Binary Decision Diagram) [20] is used to represent the values on wires as functions of the symbolic values. In practice, it is the users choice to decide on conventional simulation, X-simulation or symbolic simulation. In conventional simulation we have to exercise test runs one by one, which is a time consuming process. Assigning an input to X in X-simulation reduces the number of simulation runs, but loses the information so that simulation results might not be useful. Symbolic simulation also reduces the number of simulation runs and does not lose information, but too many symbolic values will make the BDDs too large to build. Symbolic model checking means using BDDs in the model checking algorithm. Model checking lets us verify that a state machine or formal model obeys a property we specify using temporal logic. The key idea is to systematically explore the state space of a finite state machine in order to check that the given temporal logic formula holds of a machine. The detailed explanation on temporal logic is postponed to next chapter. In simple words symbolic model checking [21, 22, 23, 24] typically uses the symbolic simulation algorithm based on BDDs. Ken McMillan et al. were the first to create a publicly available symbolic model checker based on BDDs [25]. The detailed explanation on BDDs is deferred to the next chapter.

It is accepted that *symbolic model checking* is suited for verifying hardware systems and *explicit state model checking* has advantages of verifying concurrent or asynchronous software [26].

#### 1.3.3.3 Bounded Model Checking based on SAT Solvers

In bounded model checking [27, 28, 29], a Boolean formula is satisfiable if and only if the underlying state transition system comprehends a finite sequence of state transitions that reaches certain states of interest. In simple words: we reduce the model checking problem to propositional satisfiability for a finite number of simulation cycles. The idea of BMC is to unroll the sequential circuit into k time-frames of a combinational circuit representing the state transition and output function, and counterexamples are searched in this unrolled system description. If no bug is found then one increases k until either a bug is found or some defined upper time bound is reached. For example, we have a transition system M, a temporal logic formula p and a time bound k. Then we construct a propositional formula, which will be satisfiable if and only if the formula f is valid along

some computation path of M with length k. A propositional formula F is formed as follows. For the state transition system M and time bound k, the unrolled transition system is

$$F = I(q_0) \wedge \bigwedge_{i=0}^{k-1} T(q_i, q_{i+1}) \wedge \bigvee_{i=0}^{k-1} p(q_i)$$

where  $I(q_0)$  is the characteristic function of the set of initial states  $q_0$ ,  $T(q_i,q_{i+1})$  is the characteristic function of the transition relation and  $p(s_i)$  is the characteristic function of the property that we wish to check. A characteristic function [6] indicates whether an element x of a set  $\mathcal A$  is part of a subset  $\mathcal B$  of  $\mathcal A$ . Characteristic functions are functional representations of a subset.

**Definition 1** (Characteristic function) *Given two sets* A *and* B *with*  $B \subseteq A$ . *A characteristic function*  $X_B : A \to B$  *is defined as*

$$X_{\mathcal{B}}(x) = \left\{ egin{array}{l} \textit{True, if } x \in \mathcal{B} \\ \textit{False, if } x \notin \mathcal{B} \end{array} \right.$$

The robustness and the capacity increase of *bounded model checking* makes it a good choice for industrial use. This is due to the fact that satisfiability solvers seldom require exponential space. Current solvers use different heuristics in order to solve the general satisfiability problems for *bounded model checking*. All of them use the Davis Putnam algorithm [30] and variants of it. However, *bounded model checking* based on satisfiability solvers is time intensive and it can only search up to a maximum depth allowed by the physical memory on a single server. As the search bound k becomes larger, the memory requirement due to unrolling of the design also increases.

#### 1.3.3.4 BDD vs SAT

Comparing BDD and SAT based *model checking* approaches, each technique has its own advantages and disadvantages. For some particular type of designs BDD based model checkers outperform SAT based model checkers. For others, it is vice-versa. It is greatly a debatable topic to compare both approaches. Therefore, it is the user's choice to select which mechanism to follow. In [31, 32], the authors made comparisons between different approaches and inferred that more synergy can be achieved by combining both techniques.

## 1.3.4 State Explosion Problem

Formal verification methods reach their limitations very fast. As aforementioned in section 1.2 the state space of the system grows exponentially with respect to the number of flip-flops present in the design. Even a small circuit with 4 registers, each 32 bit wide, exceeds the treatable amount of state space. This is know as

Figure 1.5: Overview of thesis focus

the *state explosion* problem. Therefore, it is impossible to explore the entire state space of the system with limited resources of time and memory. Over the years considerable effort has been made in dealing with this prevalent problem. Albeit researchers have made noticeable progress to deal this problem [33, 34, 35, 31], for larger designs the problem still persists.

#### 1.3.5 Thesis Focus

This thesis will focus mainly on formal verification. To be more specific, symbolic model checking based on BDDs. Formal verification provides the exhaustive coverage and has the calibre to uncover subtle bugs in comparison with traditional simulation. However, for large industrial designs these techniques do not scale well due to the *state explosion* problem. One way to handle this problem is to use sequential based partitioned approaches. For large designs either they consume more time or postpone the *state explosion* problem. One feasible solution is to parallelize the BDD based symbolic model checking algorithm. Fig. 1.5 delineates the wider picture of the thesis focus. If the generic model checker has problems with time or memory then we can enable the parallel version of the symbolic model checker.

#### 1.3.6 Distributed Verification

Two approaches can be considered in fighting the state explosion problems [36]: clever methods or brute-force methods.

The first category can use any of the following methods:

- 1. Design of better modeling languages (small languages, formal semantics, built-in abstractions, compositionality properties) [37, 38, 39]

- 2. Invention of better verification algorithms by operating on higher-level models (abstractions, data flow analysis, reductions) or by exploiting [40, 41] structural information or by avoiding redundancies (partial orders, symmetries) [42, 43, 44], or by using locality (bounded-memory algorithms) [45].

The brute force methods lead to the use of a more powerful machines (increase memory and processing power to handle larger state spaces or use a supercomputer) or the use of several machines instead of one (combine the resources of several machines). In an ideal case, using n machines can solve the problem n times faster.

Often, people have access to large parallel computers, but cannot make full use of them because most model checkers are designed for single processor systems. The aim in exploiting a parallel or distributed environment for verification is to extend the applicability of verification algorithms to larger and more complex systems. A parallel super computer, grid or network of workstations can provide extra resources needed to tackle realistic verification problems.

**Cluster computer:** [46] A cluster computer is a type of parallel or distributed processing system, which consists of a collection of interconnected standalone computers together as a single integrated computing resource.

A computer node can be a single or multiprocessor system (PCs, workstations, Symmetric Multi Processors (SMPs)) with memory, I/O facilities, inter connection, and an operating system. A cluster refers to two or more computers (nodes) connected together. The nodes can exist in a single cabinet or be physically separated and connected via a LAN, etc. In general two types of computer cluster systems are widely used:

**Homogeneous cluster:** A homogeneous computer cluster is a group of coupled computers of equal configurations.

**Heterogeneous cluster:** A heterogeneous cluster is a collection of machines of varying architectures.

Distributed computation can help to speed up verification by providing many CPUs that can work on the problem and provide higher aggregated memory capacity.

The main idea of a distributed algorithm is to break the verification task into pieces and assign each piece among the participating workstations. The verification process on all nodes is terminated once at least one of the nodes detected a bug or error state. This way we can achieve a parallel, iterative, and interactive

verification process. In general, computation on a smaller subset requires less memory compared to the whole set. This method enables us to find errors that are far, transitions away from the initial states. Moreover, parallel computation takes less verification time compared to the sequential approach. However, there are several factors that significantly influence the overall effectiveness of verification in the distributive environment. These factors have to dealt with a nontrivial manner as far as parallel model checking is concerned. Some of them include:

- **Load balancing:** This is a technique to spread work between many processes or other resources in order to get optimal resource utilization and to decrease computing time. With respect to model checking, each network node is assigned approximately the same number of states, thus achieving good speed-up.

- **Synchronization:** Refers to the idea that multiple processes are to join up at a certain point to ensure correctness or to reach an agreement or to commit to a certain sequence of action.

- **Communication:** Parallel processes typically need to exchange data in order to efficiently accomplish the tasks assigned to them. The lesser the communication involved, the better the parallelization we can achieve.

#### 1.4 Thesis Structure

This thesis is structured as follows:

- **Chapter 2:** Sheds light on basics that will be deployed to construct the methodologies described in the thesis.

- **Chapter 3:** Deals with state-of-the-art sequential, parallel and partitioning heuristics. Next, it discusses a few of the open problems that need to be treated. Finally, it covers the thesis contributions.

- **Chapter 4:** Describes the basic parallelization algorithm for bounded property checking. It covers the raw materials needed for the basic parallelization. It also introduces the prevalent problem called *state set overlap*.

- **Chapter 5:** Presents some techniques for treating *state set overlap*. It explicates the application of static overlap reduction on a distributive environment. The overlap can be confined to only a certain number of simulation steps using static reduction technique. Therefore a better algorithm is needed to remove the overlap. It describes a novel on-the-fly asynchronous state space traversal algorithm using *dynamic overlap reduction* technique.

- **Chapter 6:** Presents a hybrid distributed symbolic verification algorithm based on *windowing* and *dynamic overlap reduction* techniques, suited for full validation and fast falsification. The approach is mainly asynchronous.

- **Chapter 7:** Expounds a new grid based distributed bounded symbolic verification approach based on effective combination of state-of-the-art intelligent partitioning algorithms that suits best for fast falsification.

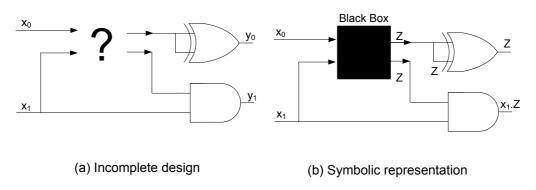

- **Chapter 8:** Elucidates the parallelization of a Black Box verification for incomplete designs. The work described in this chapter was done as a cooperative task between University of Tübingen and University of Freiburg under the research project FEST (Funktionale Verifikation von Systemen) [47] in the year 2007.

- **Chapter 9:** Explicates all the implementation details. First it explains the ingredients needed for the parallelization. Second, it explains the methods that can transfer the data between network nodes. In addition, it describes an efficient way to communicate BDD functions among network nodes. Finally, it gives the components required for the grid framework.

- Chapter 10: Gives experimental results. First it details the utilized parallel environment, designs and properties. Next, it delineates the advantage of parallel approach over sequential based verification. Then first it compares the dynamic overlap reduction and hybrid distributive approaches and second it compares the algorithms presented in thesis with state-of-the-art parallel algorithms. Finally, it presents the results using the grid based distributive approach.

- **Chapter 11:** Briefly presents the concluding remarks for this thesis and provides directions for future work.

## **Chapter 2**

## **Preliminaries**

Success is neither magical nor mysterious. Success is the natural consequence of consistently applying the basic fundamentals.

- Jim Rohn

### 2.1 Boolean Functions

A Boolean function describes how to determine a Boolean value output based on a logical calculation from Boolean inputs. It plays a crucial role in hardware verification.

**Definition 2** A Boolean function with m inputs is a mapping  $f: B^m \to B$ , where B = [0,1] is a Boolean domain and m is a positive integer.

Boolean functions are used to express formalisms in hardware verification. For example transition relations or output functions of finite state machines are Boolean functions [6]. Boolean functions can be represented in various ways, e.g. as function tables, formulas of propositional logic and graphs. A Boolean function is called *valid* if it results in the value *true* for all interpretations of Boolean variables. The function is called *satisfiable* if there exists at least one interpretation which results in the value *true*.

## 2.1.1 Support Set

**Definition 3** *The set of variables which constitute a Boolean function* f *is called support of* f.

#### 2.1.2 Minterms

**Definition 4** A Boolean function  $f: B^n \to B$ , a product term in which each of the n variables appears once (either complemented, or uncomplemented) is called a minterm.

A product term is a conjunction of literals, where each literal is either a variable or its negation

#### 2.1.3 Cofactor

**Definition 5** The cofactor of a Boolean formula f with respect to a variable v is the formula obtained by replacing every occurrence of of v in f by constant 1 and is denoted by  $f|_v$  or  $f_v$ .

$f_v$  is called as *positive cofactor* and  $f_{\overline{v}}$  is called as *negative cofactor*, where every occurrence of v in f is replaced by constant 0.

## 2.1.4 Shannon Expansion

**Definition 6** Given a Boolean function  $f: B^n \to B$ , f is partitioned into two functions  $f_1$  and  $f_2$  on a variable v.

$$f = f_1 \lor f_2$$

where  $f_1 = v \land f_v, \ f_2 = \bar{v} \land f_{\bar{v}}$

$$f_v = f \land v$$

$$f_{\bar{v}} = f \land \bar{v}$$

.

#### 2.1.5 Generalized Cofactor

**Definition 7** [6] Given two functions  $f: B^k \to B$  and  $c: B^k \to B$ , where B = [0,1]. The function co(f,c) or  $f|_c$  is called generalized cofactor f with respect to c, if the following conditions holds.

$$f\big|_c = \begin{cases} & \text{False} & \text{if c = False} \\ f & \text{if c = True} \\ & \text{True} & \text{if c = } f \\ & \text{False} & \text{if c = } \neg f \end{cases}$$

This definition can be applied to reduce the sizes of BDDs in the context of state space traversal techniques. And it will be explained in detail in later chapters of this thesis.

## 2.2 Finite State Machines

Typically sequential circuits are modeled as Finite State Machines (FSMs).

**Definition 8** A FSM  $\mathcal{M}$  is a 6-tuple  $\mathcal{A} = (S, I, \delta, \lambda, S_0, O)$ , where  $S = \{s_1, \dots, s_n\}$  is a finite set of states, I is a finite alphabet,  $\delta : S \times I \to S$  is the next state function,  $\lambda : S \times I \to O$  is the output function,  $S_0 \subseteq S$  is the initial state,  $O \subseteq S$  is a set of final states.

The formal model deals with the Boolean domain. The operators  $\land$  ,  $\lor$  ,  $\neg$ ,  $\rightarrow$  and  $\leftrightarrow$  used for Boolean conjunction, disjunction, negation and implication and equivalence respectively. Where  $a \rightarrow b$  can also be written as  $\overline{a} \lor b$  and  $a \leftrightarrow b$  can be written as  $(a \rightarrow b) \land (b \rightarrow a)$

Usually, FSMs are modelled using Mealy or Moore machines.

**Moore Machine:** A Moore machine is a state machine which uses only entry actions so that its output depends on the current state alone  $(\lambda:S\to O)$  [48]. An entry action is an action that is performed *when entering* the state. The state diagram for a Moore model will include an output signal for each state. The number of states in a Moore machine will be greater than or equal to the number of states in the corresponding Melay machine [49].

**Mealy Machine:** A Mealy machine is a state machine which uses only input actions, so that the output depends only on the current state and also on inputs  $(\lambda : S \times I \to O)$  [50]. An input action an action that is performed depending on the present state and input conditions. The use of a Mealy FSM leads often to a reduction of number of states [49].

For each Mealy machine there is an equivalent Moore machine whose states are the union of Mealy machine's states and the Cartesian product of the Mealy machine's states and the input alphabet. The choice of machine type depends on the application and personal preference of the designer.

## 2.3 Binary Decision Diagrams (BDDs)

A BDD is a data structure for representing a Boolean function. Bryant first [51] introduced BDD in its current form.

**Definition 9** *A BDD is a rooted, directed acyclic graph. Conceptually, a BDD for a Boolean function can be built, obeying the following restrictions* [52]:

- 1. One or two terminal nodes of out-degree zero labeled 0 or 1.

- 2. A set of variable nodes u of out-degree two. The two outgoing edges are given by two functions if(u) and else(u).

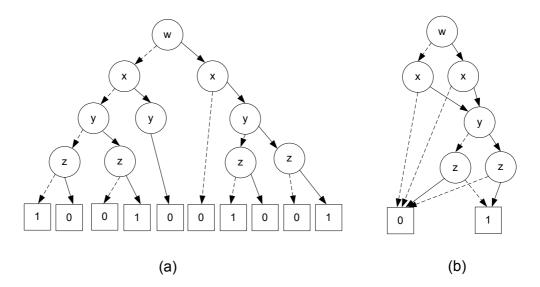

Figure 2.1: (a) An example decision diagram. (b) An ROBDD with variable ordering w < x < y < z. Dashed lines in both figures denote else branches and solid lines represent if branches.

3. Along any path from the root to a terminal node, no variable appears more than once.

**Definition 10** A BDD is ordered (OBDD) if on all paths through the graph the variables respect a given linear order  $x_1 < x_2 < ... < x_n$

Fig. 2.1 (a) shows the Boolean expression  $t = (w \leftrightarrow x) \land (y \leftrightarrow z)$  as a binary decision diagram.

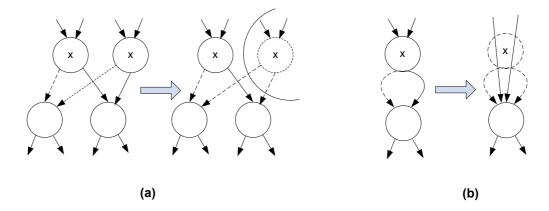

**Definition 11** A(O)BDD is Reduced (R(O)BDD) if it conformed to the following rules:

**Uniqueness:** No distinct nodes u and v have the same variable name and if and else successors are shown in Fig. 2.2 (a) , i.e.,

$$\left. \begin{array}{l} var(u) = var(v) \\ if(u) = if(v) \\ else(u) = else(v) \end{array} \right\} \Rightarrow u = v$$

**Non-redundant tests:** *No variable node u has identical if and else successor, i.e.,*

$$if(u) \neq else(u)$$

Fig. 2.2 (b) denotes this rule. ROBDDs provide compact representations of Boolean expressions. However, ROBDDs may grow exponentially with respect to the number of variables. Efficient algorithms exist for performing all kinds of operations (AND, OR, NOT, etc.) on ROBDDs.

Variable ordering: The size of an ROBDD for a Boolean function is largely influenced by the used variable ordering. However, finding an optimal ordering for a

Figure 2.2: Reduction rules for constructing the ROBDD.

given Boolean function is an NP complete problem. Fig. 2.1 (b) shows a BDD for  $(w \leftrightarrow x) \land (y \leftrightarrow z)$  with ordering w < x < y < z. Therefore, in practical applications heuristics are used. There are two kinds of heuristics available for finding variable orderings [6]: *static* and *dynamic approaches*. Static heuristics [53] derive the ordering from analyzing the structural information of the circuit before the ROBDD is constructed. Whereas, dynamic approaches [54, 55, 56, 57] make the graph more compact by changing the original variable ordering during or after the ROBDD construction. Once the variable order is fixed, a BDD is a canonical representation for a Boolean function. Every distinct Boolean function has a exactly one unique BDD representation. There exist several publicly available BDD packages [58, 59, 60]. Each package associated with functions that implement *dynamic variable reordering*, efficient vectorized BDD operations, automatic garbage collection, interfaces with different programming languages, etc.

#### 2.3.1 Notations

Let S be a state set represented using BDD. Then |S| denotes the number of BDD vertices or nodes and |S| denotes the number of states in S, which is given by the number of maximal minterms of the BDD.

#### 2.3.2 Partitioned-ROBDDs

The idea of *partitioning* was introduced and discussed extensively in [61, 62].

**Definition 12** [63] Given a Boolean function  $f: B^n \to B$ , defined over n input variables  $X_n = \{x_1, ..., x_n\}$ , the POBDD representation  $\mathcal{X}_f$  of f is a set of k function pairs,  $\mathcal{X}_f = \{(w_1, f_1), ..., (w_k, f_k)\}$  where,  $w_i: B^n \to B$ ,  $f_i: B^n \to B$  are also defined over  $X_n$  and satisfy the following conditions:

- 1.  $w_i$  and  $f_i$  are boolean functions, for  $1 \le i \le k$ .

- 2.  $w_1 \vee w_2 \vee ... \vee w_k = 1$ .

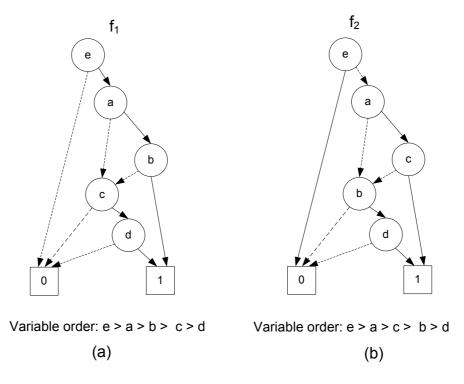

Figure 2.3: Partitioned BDDs  $f_1$  and  $f_2$

- 3.  $w_i \wedge w_j = 0$ , for  $i \neq j$ .

- 4.  $f_i = w_i \wedge f$ , for  $1 \le i \le k$ .

Each  $w_i$  is called a *window* function that can be used to partition the Boolean space over which f is defined. In Partitioned-ROBDDs the Boolean space is divided into k partitions using window functions ( $w_i \in W$ ). The functionality of f is represented over each partition as a separate ROBDD  $f_i$ . Boolean operations can be efficiently performed on them just like ROBDDs. They can be exponentially more compact than ROBDDs for certain classes of functions.

A simple example BDD f:

$$f = e \wedge \big((a \wedge b) \vee (c \wedge d)\big) \bigvee \overline{e}\big((a \wedge c) \vee (b \wedge d)\big)$$

with window functions e and  $\overline{e}$  can be partitioned into two POBDDs  $f_1$  and  $f_2$ :

$$f_1 = e \wedge ((a \wedge b) \vee (c \wedge d))$$

$$f_2 = \overline{e} \wedge ((a \wedge c) \vee (b \wedge d))$$

The Fig. 2.3 depicts the corresponding POBDDs with different variable reorderings.

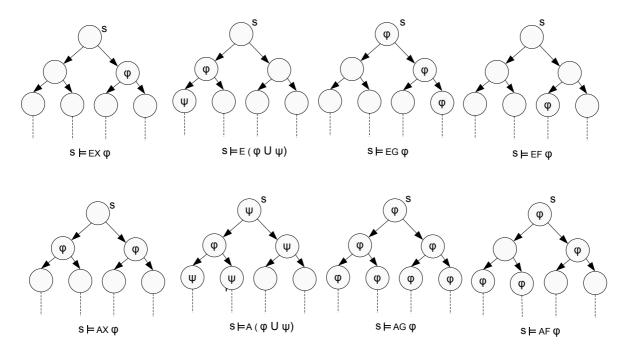

Figure 2.4: The base operators of CTL.

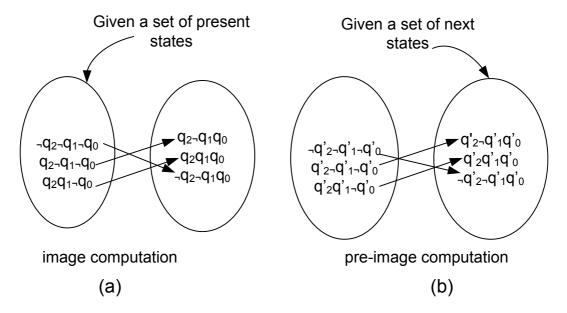

## 2.4 Temporal Logics

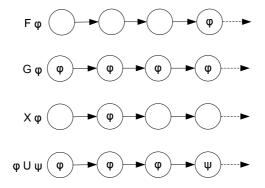

Temporal logic is a formal way of expressing properties that change over time [6]. It describes sequences of transitions between states in a reactive system [1]. More precisely the logic reason about variables with truth values which change over time. A reactive system is a system that changes its actions, outputs and conditions/status in response to stimuli from within or outside it. Temporal logics have the ability to reason about a time line. The most predominantly used temporal logic is CTL\* (Computation Tree Logic\*). It contains two sublogics CTL (Computation Tree Logic) and LTL (Linear Time Temporal Logic), which are used mostly in practice [15].

#### 2.4.1 CTL\*

CTL\* formulas describe properties of *computation trees*. The tree is formed by unwinding the Kripke structure into an infinite tree with the initial state as root. Where a Kripke structure is a type of nondeterministic finite state machine used in model checking to represent the behavior of a system. It is basically a graph whose nodes represent the reachable states of the system and whose edges represent state transitions. Temporal logics are traditionally interpreted in terms of Kripke structures.

CTL\* formulas are composed of *path quantifiers*:

• A (for all computation paths)

• E (for some computation path)

and temporal operators:

- X (next time) property holds in the next state of the path.

- F (eventually) property will hold at some state on the path.

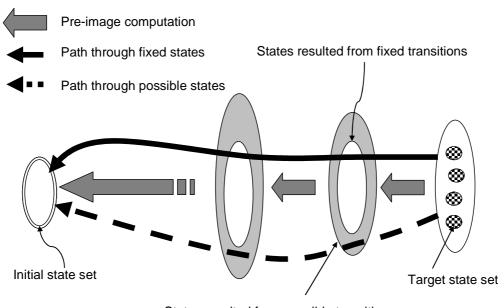

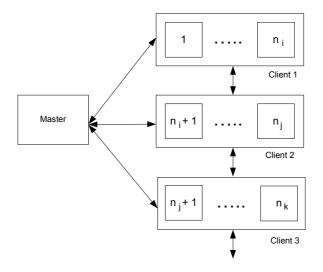

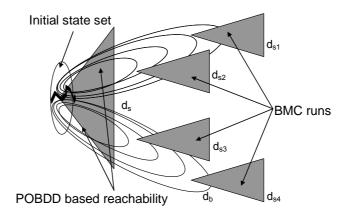

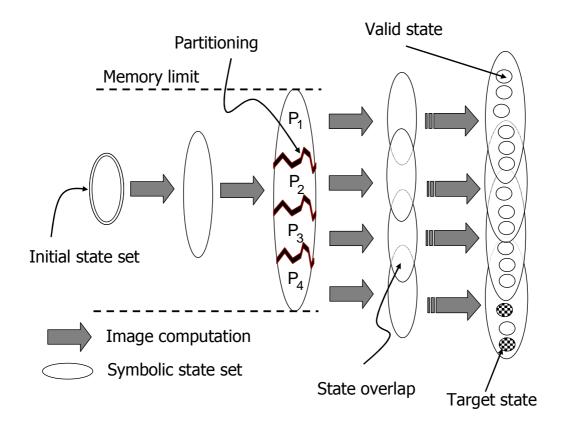

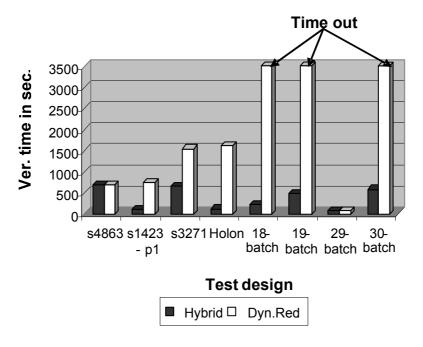

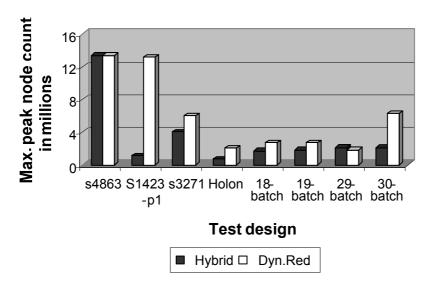

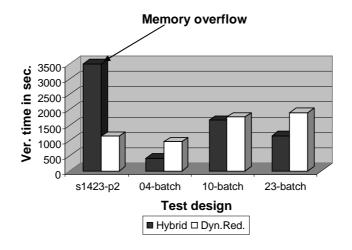

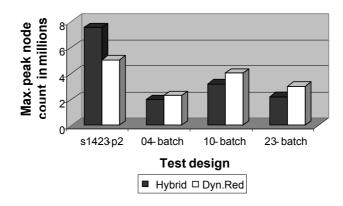

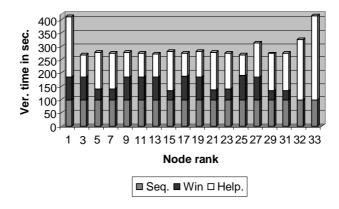

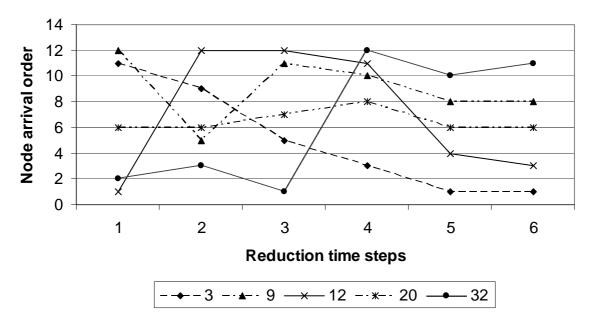

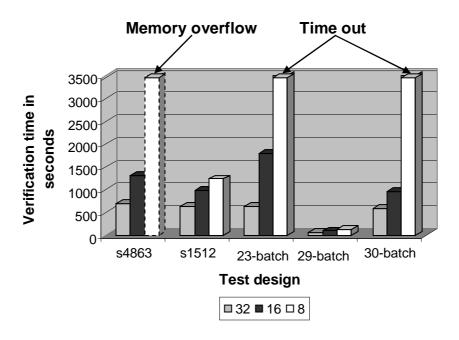

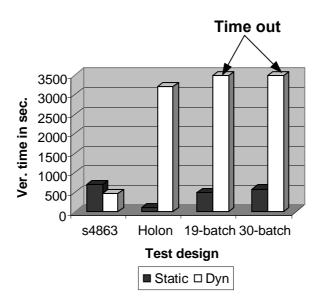

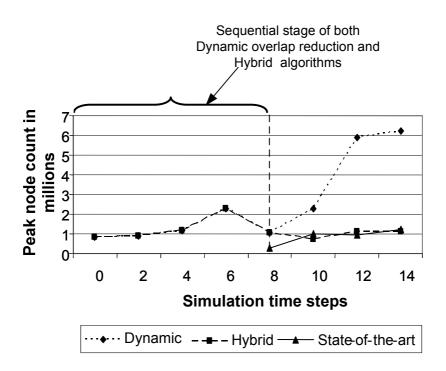

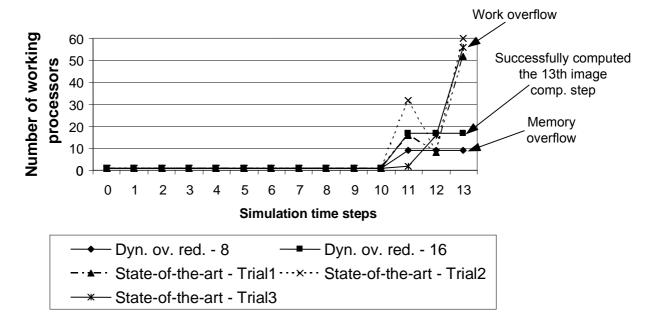

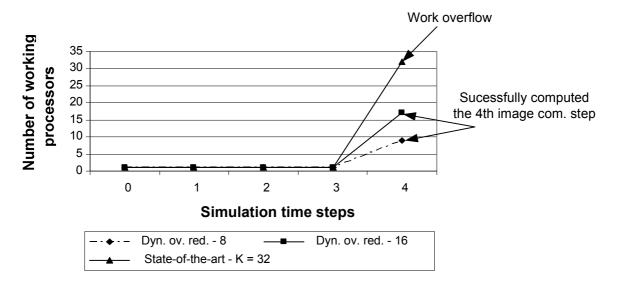

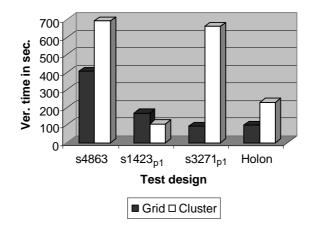

- G (globally) property holds at every state on the path.